# **PDH Switches**

Switching Technology S38.165 http://www.netlab.hut.fi/opetus/s38165

© P. Raatikainen

Switching Technology / 2004

L8 - 1

# **PDH** switches

- General structure of a telecom exchange

- Timing and synchronization

- Dimensioning example

## **PDH** exchange

- Digital telephone exchanges are called SPC (Stored Program Control) exchanges

- controlled by software, which is stored in a computer or a group of computers (microprocessors)

- programs contain the actual intelligence to perform control functions

- software divided into well-defined modular blocks, which makes the system less complicated to maintain and expand

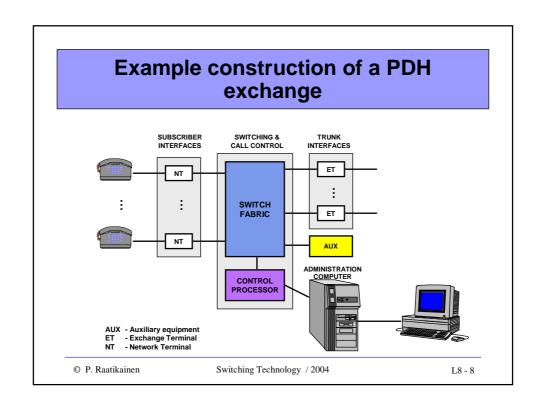

- Main building blocks

- subscriber interfaces and trunk interfaces

- · switch fabric

- switch/call control

© P. Raatikainen

© P. Raatikainen

Switching Technology / 2004

L8 - 3

L8 - 4

# Basic blocks of a PDH exchange SWITCH FABRIC SWITCH CONTROL

Switching Technology / 2004

#### **Switch control**

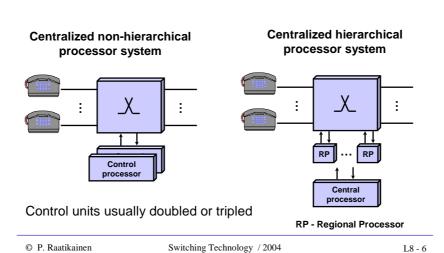

#### Centralized

- all control actions needed to set up/tear down a connection are executed in a central processing unit

- processing work normally shared by a number of processors

- hierarchical or non-hierarchical processor architecture

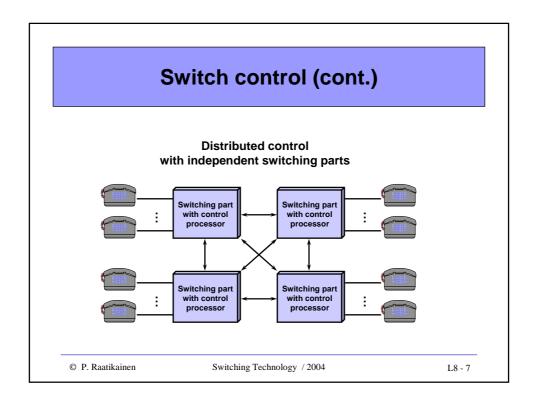

#### Distributed

- control functions are shared by a number of processing units that are more or less independent of one another

- switching device divided into a number of switching parts and each of them has a control processor

© P. Raatikainen

Switching Technology / 2004

L8 - 5

# **Switch control (cont.)**

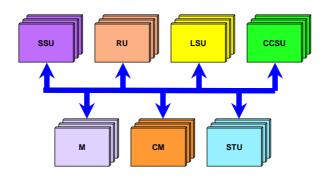

SSU

STU

CCSU - Common Channel Signaling Unit CM - Central Memory

Line Signaling Unit LSU

- Registering UnitSubscriber Stage UnitStatistics Unit

DX200 / Nokia

© P. Raatikainen

Switching Technology / 2004

L8 - 9

## **Call processing units**

- Common Channel Signaling Unit (CCSU)

- processes SS7 signaling messages

- Central Memory (CM)

- common central memory of the different control units

- Line Signaling unit (LSU)

- processes line signaling information

- Marker (M)

- connection (channel) control

- Register Unit (RU)

- registers for information such as call/customer related billing

- Subscriber Stage Unit (SSU)

- subscriber stage control (incl. subscriber signaling)

- Statistics Unit (STU)

- · statistical information such as call durations and outage periods

#### **Hierarchical control software**

Software systems in the control part:

- signaling and call control

- charging and statistics

- maintenance software

#### Control of connections:

- calls should not be directed to faulty destinations

- faulty connections should be cleared

- detected faulty connections must be reported to far-end if possible

Administration programs

Call control programs

Signaling message processing

© P. Raatikainen

Switching Technology / 2004

L8 - 11

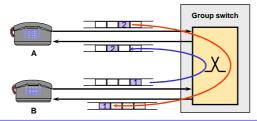

# **Switching part**

- Main task of a switching part is to connect an incoming time-slot to an outgoing one – unit responsible for this function is called a group switch

- Control system assigns incoming and outgoing time-slot, which are reserved by signaling, on associated physical links

need for time and space switching

© P. Raatikainen

Switching Technology / 2004

# **Group switch implementations**

- Group switch can be based on a space or time switch fabric

- Memory based time switch fabrics are the most common ones

- flexible construction

- due to advances in IC technology suitable also for large switch fabrics

© P. Raatikainen

Switching Technology / 2004

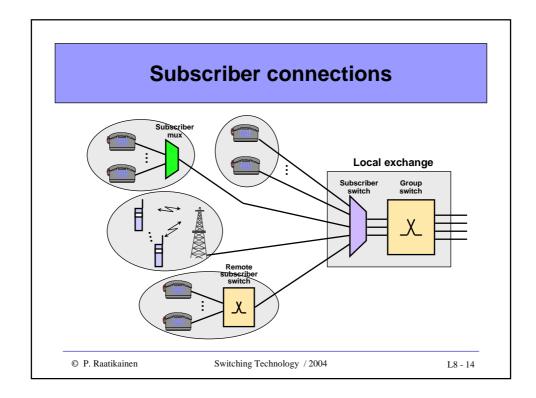

# Typical subscriber connections and trunk lines

#### Subscriber connections

- conventional twisted pair serving, e.g., an analog 3 kHz voice channel or 2B+D digital ISDN connection

- radio link serving, e.g., an analog voice channel (NMT) or a digital GSM voice/data channel

- E1, ..., E3 links connecting business users with a number of voice channels

#### Trunk lines

- standard PDH links (E1, ..., E4)

- standard SDH links (STM-1, ..., STM-16) carrying standard PDH/PCM signals

© P. Raatikainen

Switching Technology / 2004

L8 - 15

#### Subscriber and trunk interface

#### • Subscriber interface

- · on-hook/off-hook detection, reception of dialed digits

- check of subscriber line, power supply for subscriber line

- physical signal reception/transmission, A/D-conversion

- concentration

#### • Trunk interface

- timing and synchronization (bit and octet level) to line/clock signal coming from an exchange of higher level of hierarchy

- frame alignment/frame generation

- multiplexing/demultiplexing

# **Network synchronization**

#### **Need for synchronization**

- Today's digital telecom networks are combination of PDH and SDH technologies, i.e. TDM and TDMA utilized

- These techniques require that time and timing in the network can be controlled, e.g., when traffic is added or dropped from a bit stream in an optical fiber or to/from a radio-transmitted signal

- The purpose of network synchronization is to enable the network nodes to operate with the same frequency stability and/or absolute time

- Network synchronism is normally obtained by applying the master-slave timing principle

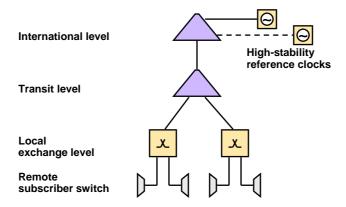

#### **Network synchronization**

#### Methods for network synchronization

- Distribute the clock over special synchronization links

- offers best integrity, independent of technological development and architecture of the network

- Distribute the clock by utilizing traffic links

- most frequently used (master-slave network superimposed on the traffic network)

- Use an independent clock in each node

- expensive method, but standard solution in international exchanges

- Use an international navigation system in each node

- GPS (Global Positioning System) deployed increasingly

- independent of technological development and architecture of network

- · Combine some of the above methods

© P. Raatikainen Switching Technology / 2004

L8 - 19

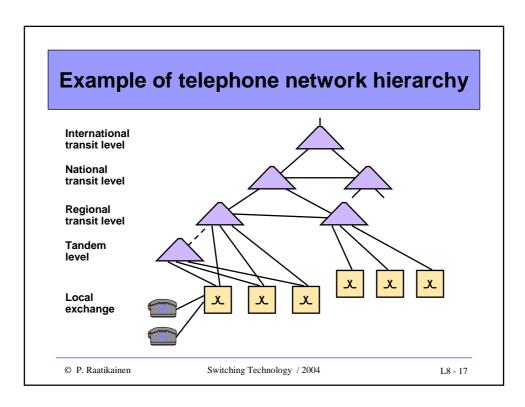

# Master-slave synchronization over transport network

ITU-T Recommendations G.810, G.811, G.812, G.812, G.823

© P. Raatikainen Switching Technology / 2004

# SDH synchronization network reference chain

- As the number of clocks in tandem increases, synchronization signal is increasingly degraded

- To maintain clock quality, it is important to specify limit to the number of cascaded clocks and set limit on degradation of the synchronization signal

- Reference chain consists of KSSUs each linked with NSECs

- Provisionally K and N have been set to be K=10 and N=20

- total number of SECs has been limited to 60

SEC - SDH Equipment Clock (accuracy 10<sup>-9</sup>) SSU - Synchronization Supply Unit (accuracy 10<sup>-6</sup>)

© P. Raatikainen

Switching Technology / 2004

L8 - 21

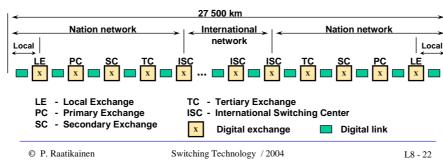

# PDH synchronization reference connection

- End-to-end timing requirements are set for the reference connection

- · Link timing errors are additive on the end-to-end connection

- By synchronizing the national network at both ends, timing errors can be reduced compared to totally plesiochronous (separate clock in each switch) operation

- International connections mostly plesiochronous

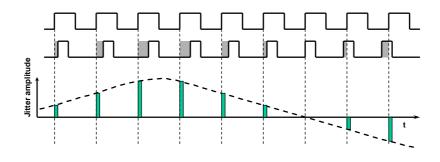

# Types of timing variation

- Frequency offset

- steady-state timing difference causes buffer overflows

- Periodic timing differences

- jitter (periodic variation > 10 Hz)

- wander (periodic variation < 10 Hz)

- Random frequency variation cased by

- electronic noise in phase-locked loops of timing devices and recovery systems

- transients caused by switching from one clock source to another

- Timing variation causes

- slips (= loss of a frame or duplication of a frame) in PDH systems

- pointer adjustments in SDH systems => payload jitter

- => data errors

© P. Raatikainen

Switching Technology / 2004

L8 - 23

# Visualization of jitter and wander

© P. Raatikainen

Switching Technology / 2004

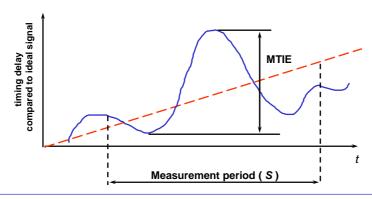

# **Timing variation measures**

- Time interval error (TIE)

- difference between the phase of a timing signal and phase of a reference (master clock) timing signal (given in ns)

- Maximum time interval error (MTIE)

- maximum value of TIE during a measurement period

- Maximum relative time interval error (MRTIE)

- underlying frequency offset subtracted from MTIE

- Time deviation (TDEV)

- average standard deviation calculated from TIE for varying window sizes

© P. Raatikainen

Switching Technology / 2004

L8 - 25

#### **Maximum time interval error**

Maximum of peak-to-peak difference in timing signal delay during a measurement period as compared to an ideal timing signal

© P. Raatikainen

Switching Technology / 2004

# MTIE limits for PRC, SSU and SEC

| Clock<br>source | Time-slot<br>interval [ns]                                                             | Observation interval                                                     |

|-----------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| PRC             | 25 ns<br>0.3 <i>t</i> ns<br>300 ns<br>0.01 <i>t</i> ns                                 | 0.1 < t < 83 s<br>83 < t < 1000 s<br>1000 < t < 30 000 s<br>t > 30 000 s |

| SSU             | 25 ns<br>10 <i>t</i> ns<br>2000 ns<br>433 <i>t</i> <sup>0,2</sup> + 0.01 <i>t</i> ns   | 0.1 < t < 2.5 s<br>2.5 < t < 200 s<br>200 < t < 2 000 s<br>t > 2 000 s   |

| SEC             | 250 ns<br>100 <i>t</i> ns<br>2000 ns<br>433 <i>t</i> <sup>0.2</sup> + 0.01 <i>t</i> ns | 0.1 < t < 2.5 s<br>2.5 < t < 20 s<br>20 < t < 2 000 s<br>t > 2 000 s     |

ETS 300 462-3

© P. Raatikainen

Switching Technology / 2004

L8 - 27

# Occurrence of slips

- Slips occur on connections whose timing differs from the timing signal used by the exchange

- If both ends of a connection are internally synchronized to a PRC signal, theoretically slips occur no more frequently than once in 72 days

- In a **reference connection**, a slip occurs theoretically once in 72/12 = 6 days or if national segments are synchronized once in 72/4 = 18 days

- Slip requirement on an end-to-end connection is looser:

| Average frequency of slips | Share of time during one year |  |

|----------------------------|-------------------------------|--|

| ≤ 5 slips / 24h            | 98.90 %                       |  |

| 5 slips/ 24 h 30 slips/ 1h | < 1 %                         |  |

| ≤ 10 slips / 1h            | < 0.1 %                       |  |

© P. Raatikainen

Switching Technology / 2004

#### Slip calculation example

Show that two networks with single frame buffers and timed from separate PRCs would see a maximum slip rate of one slip every 72 days

#### Solution:

- Timing accuracy of a PRC clock is 10<sup>-11</sup>

- Let the frequencies of the two ends be f<sub>1</sub> and f<sub>2</sub>

- In the worst case, these frequencies deviate from the reference clock f<sub>o</sub> by 10<sup>-11</sup>x f<sub>o</sub> and those deviations are to different directions

- Let the frequencies be  $f_1 = (1 + 10^{-11}) f_0$  and  $f_2 = (1 10^{-11}) f_0$

- Duration of bits in these networks are  $T_1$ = 1/  $f_1$  and  $T_2$ = 1/  $f_2$

© P. Raatikainen

Switching Technology / 2004

L8 - 29

## Slip calculation example (cont.)

#### Solution (cont.):

- During one bit interval, the timing difference is |T<sub>1</sub>-T<sub>2</sub>| and after some N bits the difference exceeds a frame length of 125 µs and a slip occurs =>  $N|T_1 - T_2| = 125 \times 10^{-6}$

- $=> N = 125 \times 10^{-6} / [|T_1 T_2|] = 125 \times 10^{-6} / [|(1/f_1 1/f_2)|]$

- Inserting  $f_1 = (1 + 10^{-11}) f_0$  and  $f_2 = (1 10^{-11}) f_0$  into the above equation, we get =>  $N = 125 \times 10^{-6} f_0 (1 - 10^{-22})/(2 \times 10^{-11}) = 62.5 \times 10^{-5} \times f_0$

- Multiplying N by the duration (T<sub>b</sub>) of one bit, we get the time (T<sub>slip</sub>) between slips

- In case of E1 links,  $f_0 = 2.048 \times 10^6 / \text{s}$  and  $T_h = 488$  ns. Dividing the obtained  $T_{\text{slip}}$  by 60 (s), then by 60 (min) and finally by 24 (h) we get the average time interval between successive slips to be 72.3 days

#### Synchronization of a switch

#### Synchronization sub-system in an exchange

- Supports both plesiochronous and slave mode

- Clock accuracy is chosen based on the location of the exchange in the synchronization hierarchy

- accuracy decreases towards the leaves of the synchronization tree

- Synchronizes itself automatically to several PCM signals and chooses the most suitable of them (primary, secondary, etc.)

- · Implements a timing control algorithm to eliminate

- instantaneous timing differences caused by the transmission network (e.g. switchovers - automatic replacement of faulty equipment with redundant ones)

- jitter

- Follows smoothly incoming synchronization signal

© P. Raatikainen

Switching Technology / 2004

L8 - 31

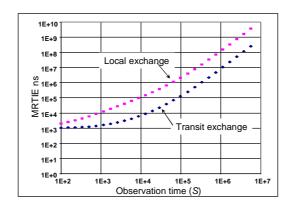

# Synchronization of a switch (cont.)

#### **Exchange follows the synchronization signal**

- Relative error used to set requirements

- maximum relative time interval error MRTIE≤1000 ns (S≥ 100s)

- Requirement implies how well the exchange must follow the synchronization signal when the input is practically error free

- When none of the synchronization inputs is good enough, the exchange-clock automatically switches over to plesiochronous operation

- In plesiochronous mode MRTIE≤ (aS +0.5bS² + c) ns

- Timing system monitors all incoming clock signals and when a quality signal is detected, the system switches over back to slave mode (either manually by an operator command or automatically)

© P. Raatikainen

# Stability of an exchange clock

- Clock stability is measured by aging (= b)

- temperature stabilized aging in the order of  $n \times 10^{-10}$ /day

- MRTIE  $\leq$  (aS +0.5bS<sup>2</sup> + c) ns

- S = measurement period

- a = accuracy of the initial setting of the clock

- b = clock stability (measured by aging)

- c = constant

|   | Transit node clock                                                        | Local node clock                                                     |

|---|---------------------------------------------------------------------------|----------------------------------------------------------------------|

| а | 0.5 - corresponds to an initial frequency shift of 5x10 <sup>-10</sup>    | 10.0 - corresponds to an initial frequency shift of 1x10-8           |

| b | 1.16x10 <sup>-5 -</sup> corresponds<br>to aging of 10 <sup>-9</sup> /days | 2.3x10 <sup>-4</sup> - corresponds<br>to aging of 2x10 <sup>-8</sup> |

| С | 1000                                                                      | 1000                                                                 |

© P. Raatikainen

Switching Technology / 2004

L8 - 33

# MRTIE in an exchange (plesiochronous mode)

Duration of a time-slot in an E1 PCM-signal is  $3.9\,\mu s$  and duration of a bit is 488 ns.

© P. Raatikainen

Switching Technology / 2004

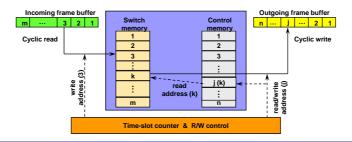

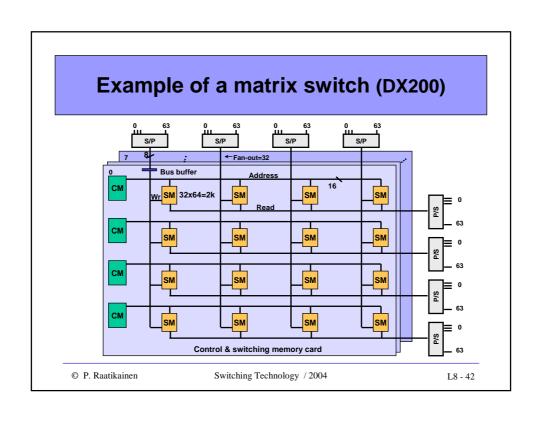

# Example of SRAM based PDH switch fabric (cont.)

#### Memory size and speed requirement:

- Switch memory (SM) and control memory (CM) are both single chip solutions

- Size of both SM and CM ≥ 64x32 octets = 2048 octets

- Number of SM write and read cycles during a frame interval (125  $\mu$ s) is 2x64x32 = 4096

- Access cycle of SM should be  $\leq$  125  $\mu s$  / 4096 = 30,5 ns

- Number of CM write and read cycles during a frame interval (125  $\mu$ s) is 1x64x32 = 2048

- Access cycle of CM should be  $\leq$  125  $\mu s$  / 2048 = 61 ns

#### PDH bit rates and related bit/octet times

| Hierarchy<br>level | Time-slot interval [ns] | Bit interval [ns] |

|--------------------|-------------------------|-------------------|

| E1/2M              | 3906                    | 488               |

| E2/8M              | 947                     | 118               |

| E3/34M             | 233                     | 29                |

| E4/140M            | 57.4                    | 7.2               |

- When time-slots turn into parallel form (8 bits in parallel) memory speed requirement decreased by a factor of 8

- Present day memory technology enables up to 256 PDH E1 signals to be written to and read from a SRAM memory on wire speed

© P. Raatikainen

Switching Technology / 2004

L8 - 37

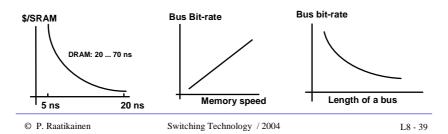

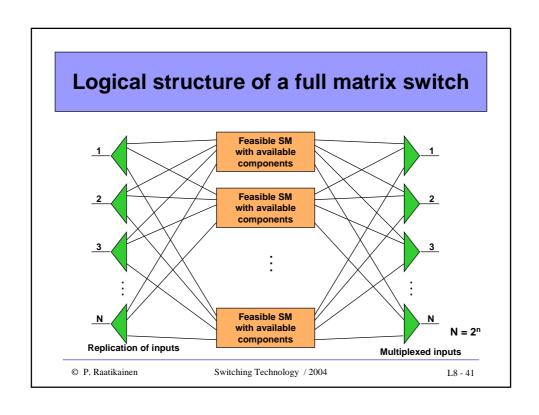

# **Properties of full matrix switches**

#### **Pros**

- strict-sense non-blocking

- no path search a connection can always be written into the control memory if requested output is idle

- · multi-cast capability

- · constant delay

- multi-slot connections possible

#### Cons

- switch and control memory both increase in square of the number of input/outputs

- broadband required memory speed may not be available

#### Make full use of available memory speed

- · At the time of design, select components that

- give adequate performance

- will stay on the market long enough

- are not too expensive (often price limits the use of the fastest components)

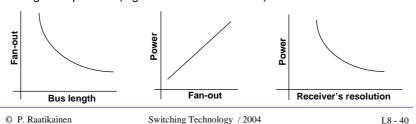

- To make full use of available memory speed, buses must be fast enough

- When increasing required memory speed, practical bus length decreases (proportional to inverse of speed)

# Power consumption - avoid heating problem

- · Power consumption of an output gate is a function of

- inputs connected to it (increased number of inputs => increased power consumption)

- bit rate/clock frequency (higher bit rate => increased power consumption)

- bus length (long buses inside switch fabric => increased power consumption and decreased fan-out)

- Increase in power consumption => heating problem

- Power consumption and heating problem can be reduced, e.g. by using lower voltage components (higher resolution receivers)

#### **Example of a matrix switch (cont.)**

- S/P (Serial/Parallel conversion) incoming time-slots are turned into parallel form to reduce the speed on internal buses

- **P/S** (Parallel/Serial conversion) parallel form output signals converted back to serial form

- 64 PCM S/P-P/S pairs implemented on one card, which is practical because PCMs are bi-directional

- One switch block can serve max 4 S/P-P/S pairs which is chosen based on required capacity (64, 128, 192 or 256 E1/PCMs)

- One S/P+P/S pair feeds max 8 parallel switch blocks chosen based on the required capacity in the installation (n \* 256 E1/PCM's)

- Max size of the example DX200-system fabric is 2048 E1/PCM's

- Currently, a bigger matrix (8K E1/PCM's) is available, slightly different SRAMs are needed, but principle is similar

© P. Raatikainen

Switching Technology / 2004

L8 - 43

#### **Example of a matrix switch (cont.)**

- A time-slot is forwarded from an S/P to all parallel switch blocks and (in each switch block) it is written to all SMs along the vertical bus

- A single time-slot replicated into max 4x8=32 locations

- Data in CMs directs storing of a time-slot in correct positions in SMs

- CM also includes data which directs reading of a correct time-slot to be forwarded to each output time-slot on each output E1 link

- CM includes a 16-bit pointer to a time-slot to be read

- 2 bits of CM content point to an SM chip and

- -5+6=11 bits point to a memory location on an SM chip

- remaining 3 bits point to (source) switch block

#### **Example of a matrix switch (cont.)**

- Number of time-slots to be switched during a frame (125 μs):

8x4x64x32 = 65 536 time-slots (= 64 kbytes)

- Each time-slot stored in 4 SMs in each of the 8 switch blocks => max size of switch memory 8x4x65 536 = 2097152 (= 2 Mbytes)

- Every 32nd memory location is read from SM in a max size switch => average memory speed requirement < 31 ns (less than the worst case requirement 64x32 write and 64x32 read operations during a 125 μs period)

- Control memory is composed of 4x4 control memory banks in each

of the 8 switch blocks and each memory bank includes 2.048

kwords (word= 2 bytes) for write and 2.048 kwords for read control,

i.e. max CM size is 8x4x4x8kbytes = 1048576 bytes (= 1 Mbytes)

© P. Raatikainen

Switching Technology / 2004

L8 - 45

#### **Growth of matrix** \_\_\_\_ 256 PCM 512 PCM © P. Raatikainen Switching Technology / 2004 L8 - 46