## **Dimensioning example**

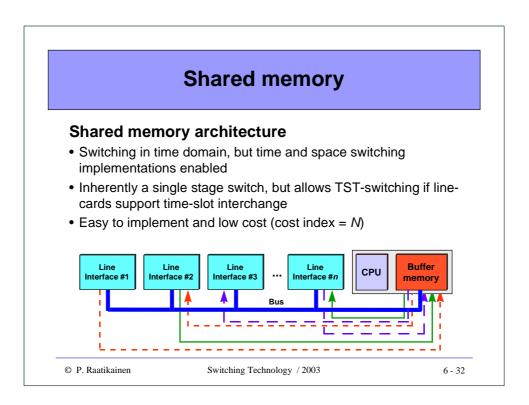

A shared memory architecture, which uses a shared bus to connect line interfaces to the memory, is used to implement a switching equipment. The bus is 32 bits wide and bus clock is 150 MHz. Three clock cycles are needed to transfer a 32 bit word through the bus and 20 % of the bus capacity is used for other than switching purposes. How many E1 interfaces can be supported by the switch ? What is the required memory speed ?

## Solution:

If the bus transfers an eight bit time-slot (of a 64 kbit/s PDH channel) across the bus at a time, a single bus solution can transfer  $0.8\times(150/3)$  Mbytes/s = 40 Mbytes/s

© P. Raatikainen

Switching Technology / 2003

6 - 35